When designing high-speed or power electronics circuits, even small inductances can create big problems. Decoupling capacitors and bondwires are key components, and modeling their real-world behavior is essential.

Equivalent Series Inductance (ESL) in capacitors and the tiny inductance of bondwires can cause voltage spikes, ringing, and noise. Ignoring them can make your simulations unrealistic.

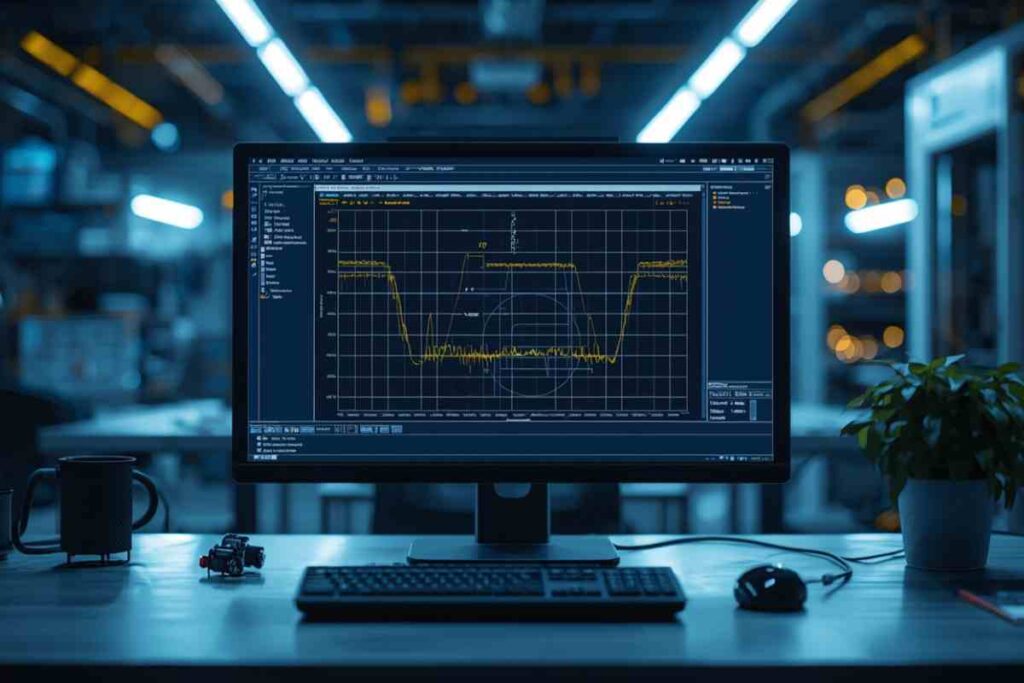

LTspice is a free, widely-used tool that lets you simulate these effects. With it, you can test designs, predict circuit behavior, and prevent surprises before building hardware.

What is ESL and Why it Matters in Decoupling Capacitors

ESL stands for Equivalent Series Inductance. It comes from the internal structure of a capacitor, including leads and packaging.

In high-speed circuits, ESL can produce voltage spikes and unwanted oscillations. For example, a switching regulator output might show smooth voltage in an ideal capacitor model, but real capacitors with ESL can produce sharp transient spikes.

Visual Example: Imagine a capacitor as a tiny spring. The more it resists sudden changes, the more your voltage overshoots during fast pulses.

How to Model Decoupling Capacitors in LTspice

Adding ESL and ESR in LTspice

Follow these steps to add real-world capacitor behavior:

- Insert a capacitor symbol in your LTspice schematic.

- Double-click it and enter the Series Inductance (Ls) value.

- Optionally, set the Equivalent Series Resistance (ESR).

- If available, use manufacturer-provided SPICE models for better accuracy—they include ESL, ESR, and parasitic capacitance.

This ensures your simulation reflects real-world responses, especially for high-frequency transients.

Practical Example: Simulating a Switching Regulator Output Cap

Try a simple step-load simulation:

- Place a decoupling capacitor with ESL and ESR.

- Apply a current step or switching pulse.

- Observe the voltage waveform at the capacitor terminals.

You may see spikes or ringing caused by ESL. Check the waveform carefully—these details show how your circuit reacts under real conditions

Understanding Bondwire Inductance

Bondwires are tiny metal wires connecting an IC die to its package pins. Even though they’re small, they have inductance—usually around 1 nH per millimeter.

Think of them as tiny springs in your circuit. When current changes rapidly, they can produce overshoot, ringing, and EMI. Neglecting bondwire inductance can make your simulation overly optimistic.

How to Model Bondwire Inductance in LTspice

- Add a small inductor in series with the power or signal pin.

- Set the inductance value based on the wire length (≈1 nH/mm).

- Optionally, for advanced setups, use behavioral models or coupled inductors if multiple wires share magnetic paths.

Proper placement and realistic values help your simulation match real hardware performance.

Combining Decap ESL and Bondwire Inductance in Simulation

Here’s a beginner-friendly workflow to simulate a realistic power path:

- Place your decoupling capacitor with ESL and ESR values.

- Add bondwire inductors in series with IC pins.

- Apply transient or AC loads to simulate operating conditions.

- Run simulations and check voltage waveforms at critical nodes.

- Adjust ESL or bondwire values and rerun for more accurate results.

Troubleshooting Tips:

- If spikes look unrealistic, check your ESL and inductor values.

- Convergence errors may appear in fast transients; reduce time step or use .TRAN options.

Advanced Tips for Accurate Power Integrity Modeling

- Non-linear inductors: For traces or power inductors that saturate, LTspice supports non-linear models. Bondwires don’t saturate, but other inductors might.

- Mutual inductance: Coupled inductors can approximate magnetic coupling between wires.

- Step-analysis: Use

.stepto see how changing ESL or inductance affects waveforms. - Cross-check with measurements: Always compare simulation results with prototype tests to confirm accuracy.

Common Mistakes to Avoid in LTspice Modeling

- Ignoring ESL or bondwire inductance entirely.

- Using only ideal capacitors.

- Skipping waveform inspection during fast transients.

- Not using manufacturer SPICE models when they are available.

Avoiding these mistakes ensures your simulation is closer to real-world performance.

Conclusion

Modeling decoupling capacitor ESL and bondwire inductance is critical for reliable, high-speed, and power electronics design.

By simulating these effects in LTspice, you can predict spikes, ringing, and noise before building hardware. Follow step-by-step workflows, adjust values carefully, and compare with real measurements. Even small inductances can have significant impacts in fast circuits.

FAQs

What is the typical ESL value for common capacitors?

It usually ranges from 0.5 nH to several nH depending on package size and type.

How do I measure bondwire inductance for LTspice?

Estimate using wire length (~1 nH/mm) or consult package datasheets.

Can I use LTspice default capacitor models for high-speed circuits?

Default models are ideal and ignore ESL/ESR—real-world behavior may differ.

How does ESR affect voltage spikes?

ESR dampens overshoot and reduces high-frequency ringing in capacitors.

Why do my simulations show unrealistic ringing?

Check ESL and bondwire values, load step size, and convergence settings.

How do I combine multiple inductors in LTspice?

Connect them in series or parallel as needed, or use coupled inductor models for mutual effects.

Are manufacturer SPICE models always better?

Yes, they include real ESL, ESR, and parasitics for accurate simulations.

Can I simulate mutual inductance between IC pins?

Yes, using coupled inductors with the K directive approximates shared magnetic paths.